排序

VSCode配合Vivado进行功耗分析(优化设计,降低能耗)

使用vscode配合vivado进行功耗分析可有效优化fpga设计。1. 配置环境:安装vivado和vscode,并配置verilog/vhdl插件及代码格式化工具;2. 设置vivado工程:完成综合与实现并生成bitstream;3. 进...

VSCode如何集成FPGA开发工具链 VSCode硬件描述语言开发的配置指南

安装verilog/vhdl/tcl等语言扩展以获得语法高亮、自动补全和代码格式化功能;2. 配置语言服务器(如svls或ghdl)以实现智能跳转、引用查找和错误检查;3. 在.vscode/tasks.json中定义任务,通过...

怎样用Java操作FPGA?JNA硬件交互

用java操作fpga的核心在于通过jna调用本地库实现与硬件的通信,具体步骤如下:1. 使用vhdl或verilog开发fpga程序并生成bitstream文件;2. 编写c++/c++驱动程序以实现java与fpga之间的指令转换;...

全平台轻量开源verilog仿真工具iverilog+GTKWave使用教程

1. 前言 如果你只是想检查Verilog文件的语法是否有错误,然后进行一些基本的时序仿真,那么Icarus Verilog 就是一个不错的选择。相比于各大FPGA厂商的IDE几个G的大小,Icarus Verilog 显得极其...

PCIe接口中断驱动寄存器被覆盖问题的发现与解决

在windows环境下使用wdf框架开发pcie驱动的dma读写功能时,启动一次dma传输需要两个步骤: 初始化DMA传输对象:在初始化DMA传输对象时,应将本次DMA传输的数据缓冲区的地址和长度写入该对象,并...

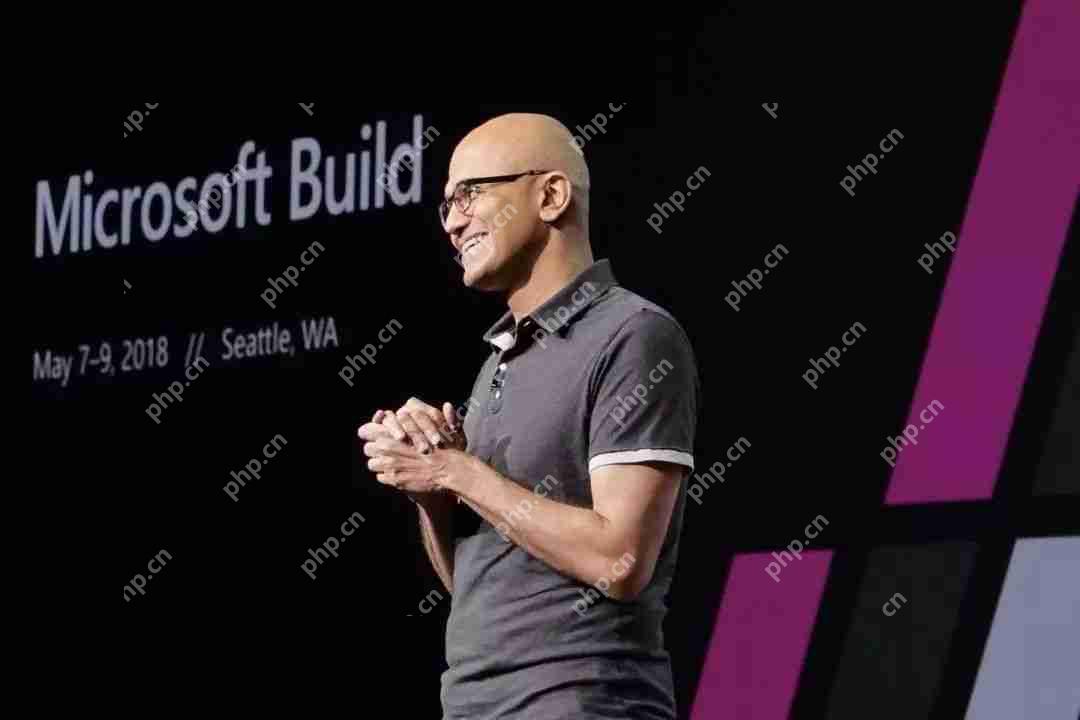

一场“正宗”的开发者大会,为什么说微软更像是“AII in AI”了?

整理 | just 出品 | AI科技大本营 众所周知,苹果的 WWDC 和 Google I/O 开发者大会通常会吸引普通消费者的关注,通过发布最新的电子消费产品来扩大影响力。 然而,微软的开发者大会却越来越专...

什么是C++中的异构计算?

异构计算在c++++中是指利用cpu、gpu等不同处理单元协同工作,以提升计算性能和效率。c++中的异构计算通过使用openmp、opencl、cuda等技术和库实现硬件协同,具体步骤包括:1) 在cpu上分配内存并...

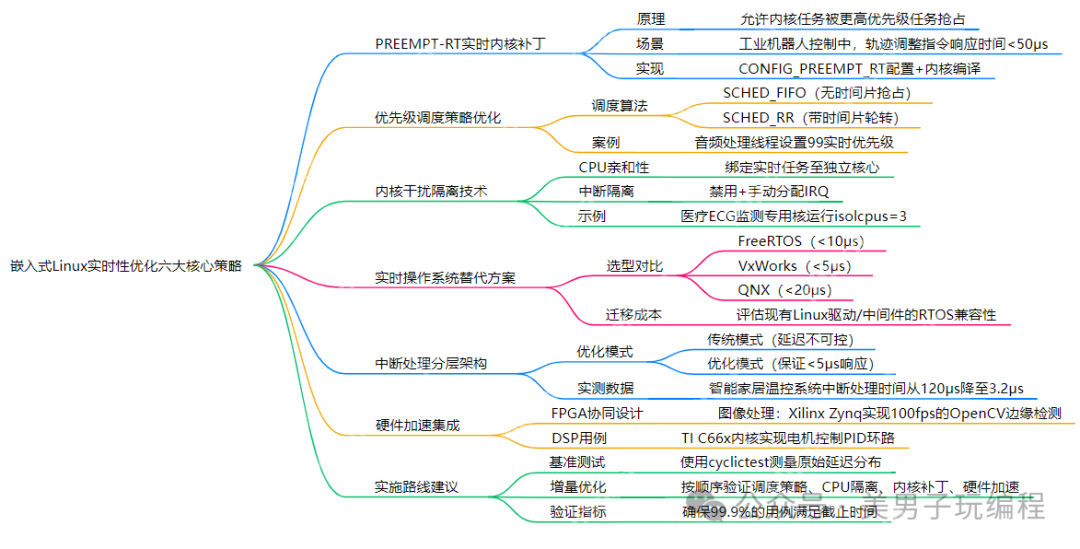

如何在Linux嵌入式系统中确保实时性?

在嵌入式系统中,尽管linux本身不是实时操作系统,但通过实施preempt-rt补丁、优化调度策略、减少内核干扰、优化中断处理以及利用硬件加速等方法,可以显著提升其实时性能。 1、应用实时Linux(...

值得收藏!sublime text3 verilog代码编写高级操作篇

下面由sublime教程栏目给大家介绍sublime text3 verilog代码编写高级操作篇,希望对需要的朋友有所帮助! 2018.10.21 好久没写博客了,这段时间一直在学习一直在沉淀,然而发现学的越多会的更少...

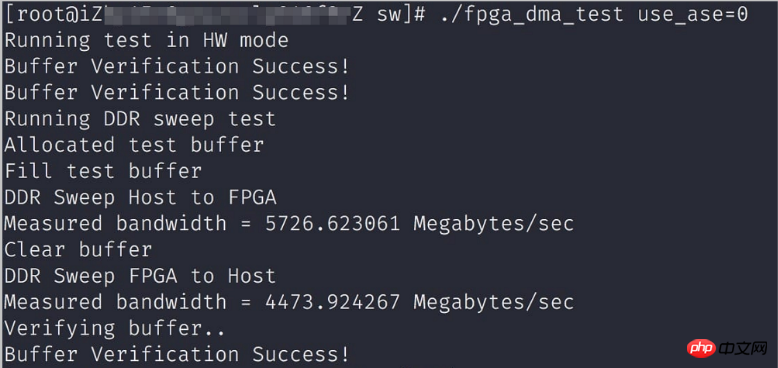

安全组中已经添加规则放行SSH端口的访问之后如何使用f1 RTL

本文在介绍安全组中已经添加规则放行ssh端口的访问之后如何使用f1 rtl的基础上,重点探讨了其具体步骤,本文内容很紧凑,希望大家耐心学习。 使用f1 RTL 本文描述如何使用f1 RTL(Register Tran...