排序

VSCode如何配置FPGA开发环境 VSCode硬件描述语言开发指南

配置vscode作为fpga开发环境的核心是安装必要插件、配置仿真与综合工具路径并熟悉语法高亮与代码补全功能;1. 安装verilog/vhdl等硬件描述语言的语法高亮和代码补全插件以提升编码体验;2. 在vs...

VSCode搭建FPGA与Python联调环境(数据交互与分析技巧)

VSCode可通过集成Python与FPGA工具链实现高效联调,核心是配置HDL支持、外部工具路径及tasks.json自动化任务,利用DPI-C或串口/USB等接口实现数据交互,并结合Python的numpy、matplotlib等库进...

VSCode配合Vivado进行IP核开发(高效工作流搭建,模块化设计)

答案:通过在VSCode中配置HDL扩展、Tcl脚本支持和Git集成,利用tasks.json调用Vivado命令实现自动化项目管理,将Vivado作为后端工具链,VSCode作为前端开发中心,提升IP核开发效率与可维护性。 ...

VSCode配置FPGA自动化脚本(TCL集成,一键编译与仿真)

首先构建清晰的项目结构并编写模块化的TCL脚本,再通过VSCode的tasks.json配置任务,实现调用TCL脚本一键完成FPGA编译与仿真。 在FPGA开发中,将VSCode配置为集成TCL自动化脚本的环境,确实能极...

VSCode配合Vivado进行FPGA图像处理(算法加速与优化)

答案:VSCode与Vivado结合可提升FPGA图像处理开发效率,前者用于代码编辑、版本控制和远程开发,后者负责综合、实现与调试,二者协同实现高效算法优化。 将VSCode与Vivado结合用于FPGA图像处理...

VSCode调试FPGA工程的技巧(结合Vivado,快速定位问题)

vscode在fpga开发中并非替代vivado,而是作为高效辅助工具提升开发效率。1. 在代码编写方面,vscode提供 superior 的语法高亮、自动补全和代码管理功能,显著优化verilog、systemverilog和tcl脚...

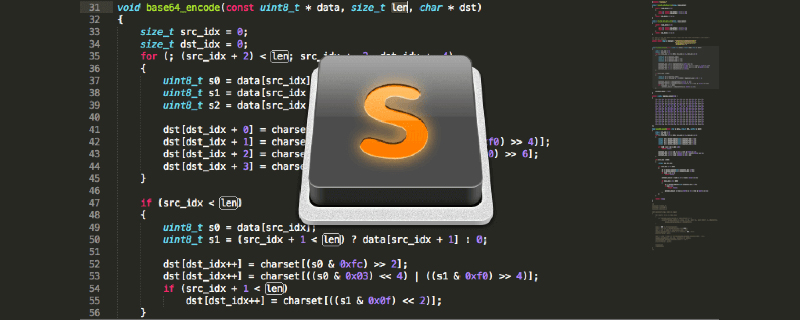

值得收藏!sublime text3 verilog代码编写高级操作篇

下面由sublime教程栏目给大家介绍sublime text3 verilog代码编写高级操作篇,希望对需要的朋友有所帮助! 2018.10.21 好久没写博客了,这段时间一直在学习一直在沉淀,然而发现学的越多会的更少...

VSCode如何集成FPGA开发工具链 VSCode硬件描述语言开发的配置指南

安装verilog/vhdl/tcl等语言扩展以获得语法高亮、自动补全和代码格式化功能;2. 配置语言服务器(如svls或ghdl)以实现智能跳转、引用查找和错误检查;3. 在.vscode/tasks.json中定义任务,通过...

VSCode调试FPGA的AXI接口(结合Vivado,总线分析技巧)

调试FPGA的AXI接口,尤其结合VSCode和Vivado,并不是说VSCode能直接像调试软件那样去“单步”硬件。这其实是一种协同作战的模式:VSCode主要负责你的软件层(无论是裸机程序、RTOS应用还是Linux...

VSCode优化FPGA代码版本控制(Git集成,团队协作规范)

FPGA项目需以VSCode+Git为核心,结合分支管理、代码审查与规范提交,实现高效协作。 FPGA项目中的代码版本控制,坦白说,一直是个让人头疼的问题。但如果能巧妙地利用VSCode和Git的强大组合,并...